平台优势

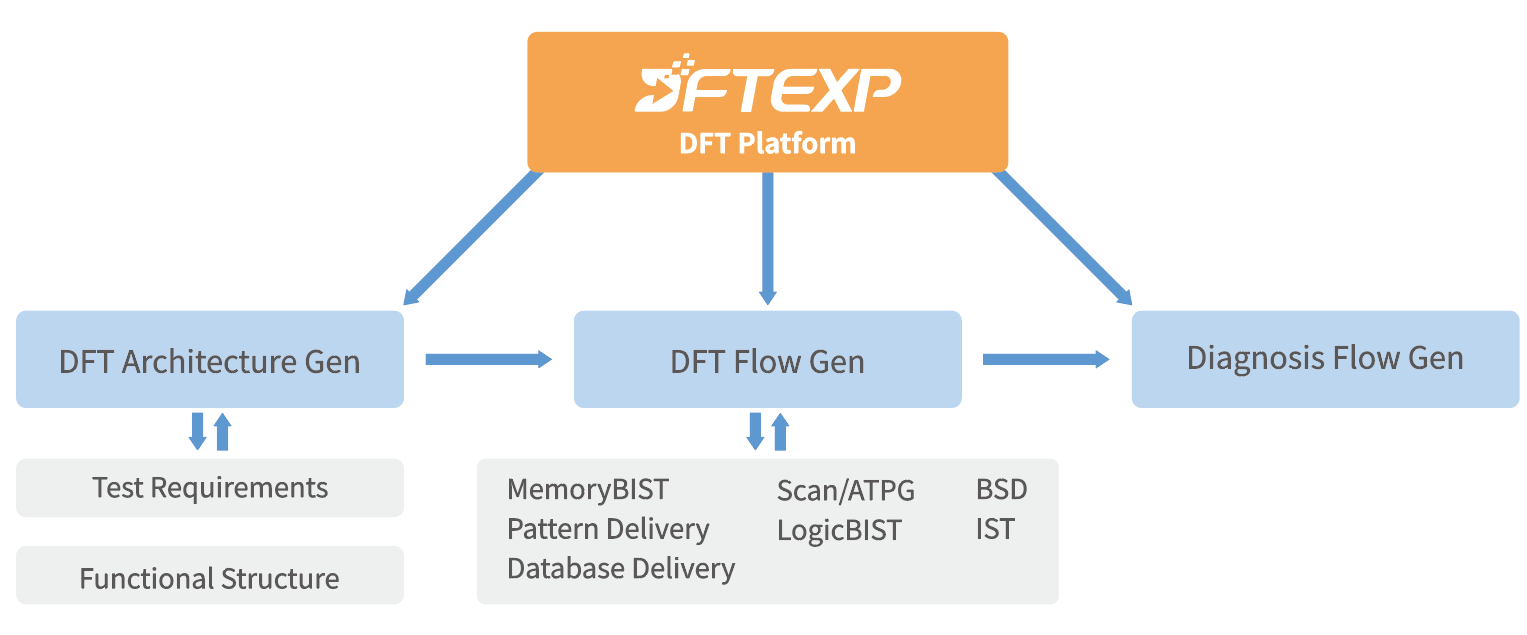

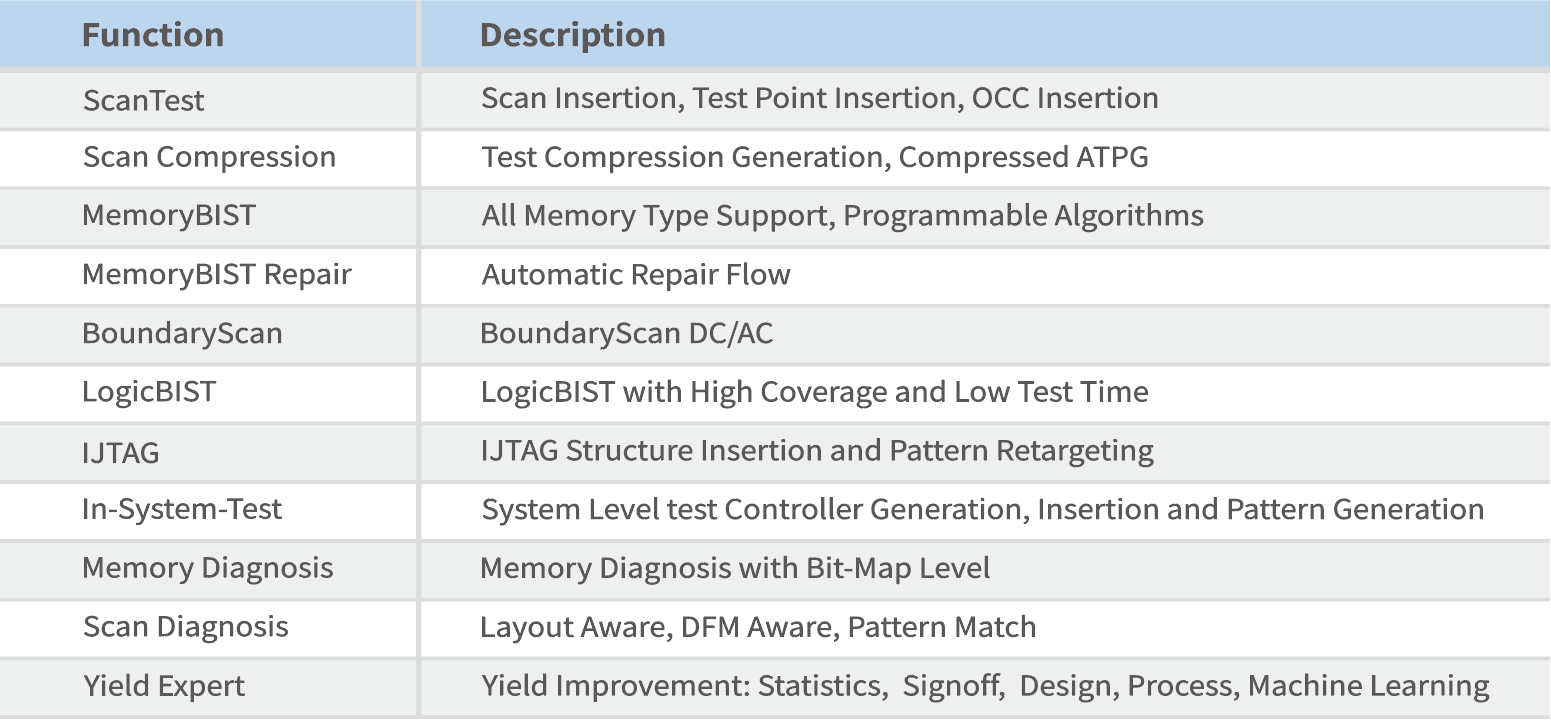

- 涵盖DFT全流程工具,支持MCU、AI、GPU、Network、5G基带、AP等不同应用领域芯片和规模的DFT设计实现需求,并且支持系统级测试的In-System-Test,以支持汽车电子的功能安全测试方案。

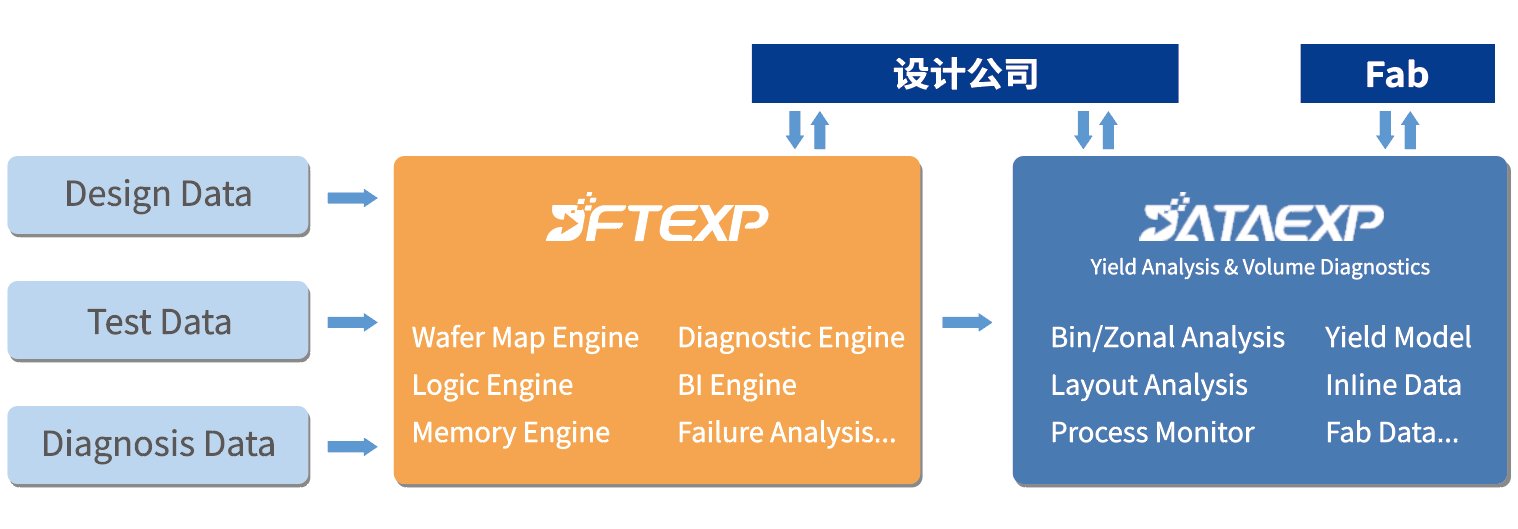

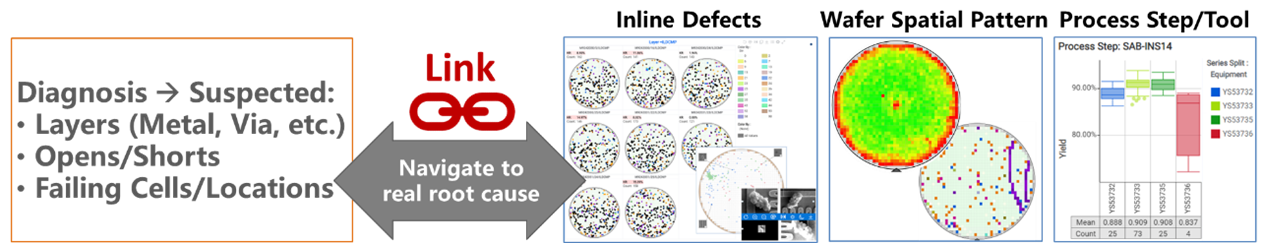

- 全方位的良率提升方案,可以适应不同工艺、不同Fab的要求。通过DFT Diagnosis和Fab 大数据分析系统,可快速发现影响良率的根因,建立提升方案。

- 从DFT的测试诊断结果,可结合DATAEXP-YMS中多维度的芯片相关数据,如产品版图、WAT/CP/FT测试数据、产线上的工艺步骤、设备、和缺陷等监控数据,从而更精准地识别故障行为和分析故障根因,加速芯片产品上市场的周期。

- DFT 自动化实现流程,以及完备的版本验收流程。同时支持RTL和Netlist Flow,并且通过HierarchicalDFT 和Hierarchical ATPG流程,加速产品Time-To-Market;建立完备的版本验收流程,满足各种工艺设计的DPPM要求。